Hummingbirdv2 E203 移植之引脚约束

上文实现了将程序固化到itcm,接下来需要将E203烧写至Xilinx Zynq UltraScale+的板子上,主要需要解决几个问题:

- 时钟:板子上的时钟是差分时钟,而且32.784kHz的时钟需要自己分频产生;

- 添加IP:pll和reset ip

- 管脚约束:需要保留的管脚有JTAG(四个),串口(gpioA[16],gpioA[17]),mcu_wakeup(连高电平)

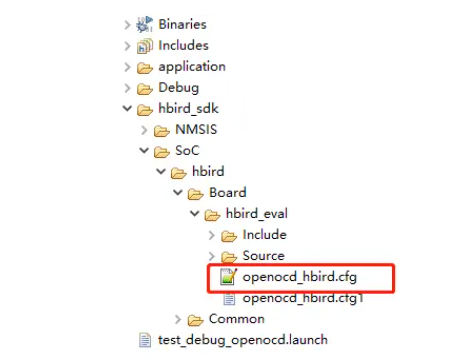

其中JTAG口是用来调试软件代码,芯来SDK工具可以将二进制软件代码通过JTAG口写入itcm,再通过串口查看打印信息。要实现这一功能,还需要在修改软件的配置信息,参见这篇博文。修改.cfg文件,注释里面包含flash的几行

一、导入文件

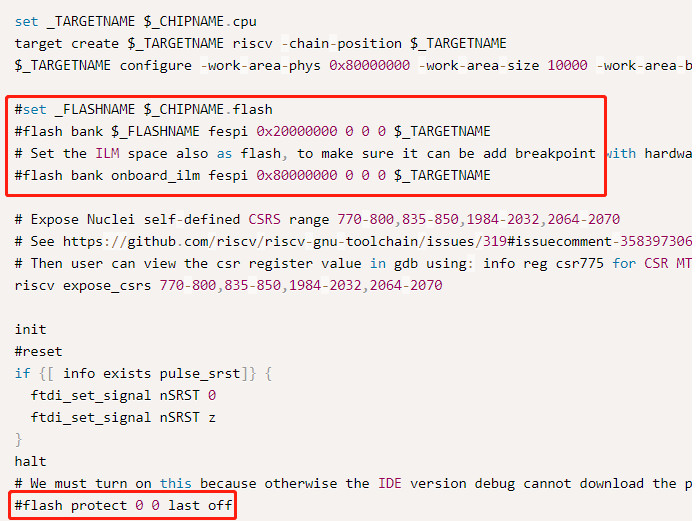

选择器件:如“xczu3eg-sfvc784-1-i” 导入顶层文件system.v,以及约束文件nuclei-master.xdc,并写一个bitstream.tcl文件:

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

否则会因为一些内部管脚没连,导致比特流文件生成出错

二、修改system.v

IO口

1、CLK100MHZ,CLK32768kHZ 改成sys_clk_p,sys_clk_n,并移入模块做wire型(之后再用pll和分频产生) 2、删除fpga_rst,随便去除后面assign语句中的fpga_rst信号 3、qspi 的相关的6个IO移入模块做wire型,并删除模块内IOBUF对其的定义 4、gpioA、gpioB移出IO,做wire型,并删除模块内IOBUF对其的定义 5、pmu两个信号移出IO,做wire型,并删除模块内IOBUF对其的定义 6、增加两个串口信号tx,rx,之后连接到gpioA[17]和gpioA[16],并在模块内增加IOBUF对其的定义

IP 添加

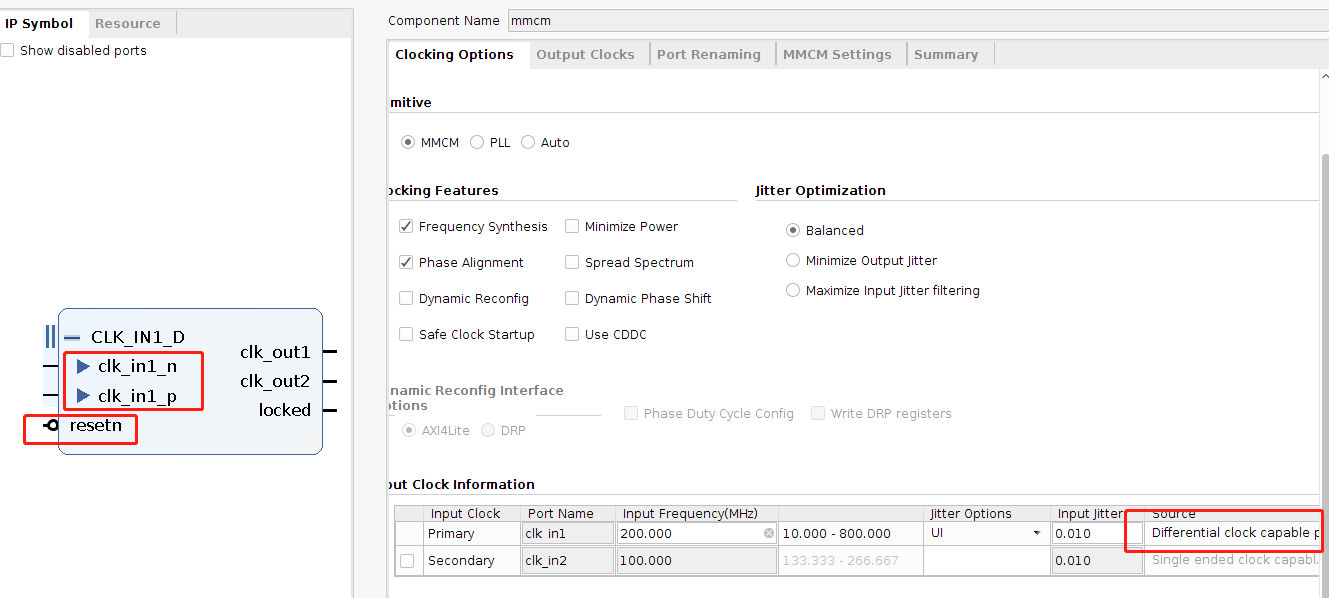

在Windows环境下用Vivado调试E203可以参考这篇文章添加缺少的mmcm和reset_sys模块。

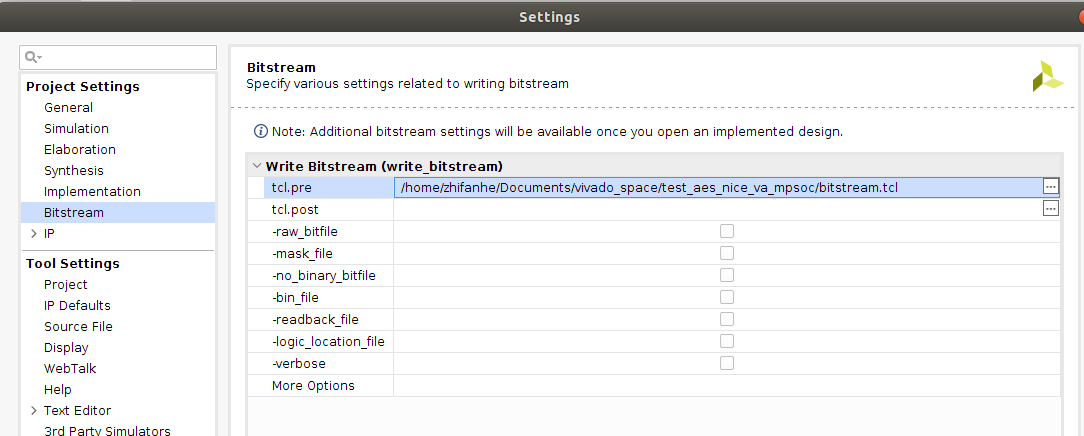

mmcm实际上就是clock wizard,我这边参考配套手册添加的:

其他重要选项

1、将信号dut_io_pads_bootrom_n_i_ival 连上1‘b0,表示从itcm中写入,非常重要。

三、管脚约束

分别设置时钟、mcu_rst、Jtag、串口、mcu_wakeup管脚。 如果综合出现e203_defines.v的错误,可以再TCL输入:

set_property file_type "Verilog Header" [get_files {your dir}/e203_defines.v]

set_property is_global_include true [get_files {your dir}/e203_defines.v]